# ОЦЕНКА ПАРАМЕТРОВ СИСТЕМЫ СИНХРОНИЗАЦИИ ДИСКРЕТНЫХ УСТРОЙСТВ ДЛЯ ЦЕЛЕЙ ДИАГНОСТИРОВАНИЯ

## Андрюхин А.И.

Кафедра ПМиИ, ДонГТУ, andr@r5.dgtu.donetsk.ua

## **Abstract**

Andruckin A.I. A system parameters evaluation of a synchronization of discrete devices for the purposes of diagnosing. A model is suggested for diagnosing and analizing of synchronization errors on the basis of boundary conditions of a mathematical programming problem. Algorithms and conditions for the model construction, linear criteria of diagnosing and examples of calculation are described.

#### Введение

Одним из основных требований при проектировании электронных схем является исключение гонок. В логических схемах встречаются участки, где сигнал разветвляется, получившиеся два сигнала распространяются по двум независимым цепочкам элементов, а затем оба сигнала снова встречаются на входах одного элемента. Пусть в тракте *T1* четное число инверторов, а в тракте *T2* - нечетное. Анализ подобной схемы на основе булевой алгебры без учета задержек даст на ее выходе 0 при любом значении входного сигнала для выходного элемента И. Но так как реальные элементы имеют конечную задержку срабатывания, то в выходном сигнале появится помеха, не предусмотренная булевыми выражениями. При достаточно большой разности *T1* и *T2* помеха будет иметь характеристики полноценного логического сигнала, который будет влиять на последующие процессы в устройстве.

Гонки по входу возникают, когда ветвящийся сигнал поступает на элементы, имеющие разброс по уровню срабатывания, а фронт этого сигнала излишне пологий. Если длительность фронта входного сигнала заметно больше времени срабатывания элементов, то где-то в середине фронта будет существовать отрезок времени, когда с точки зрения одного элемента входной сигнал уже равен 1, а с точки зрения другого—еще равен 0. Элементы будут реагировать на один и тот же сигнал как на два различных, а при такой ситуации схема в течение этого времени может выработать ложные сигналы.

Основная проблема в том, что мы не знает, в каком тракте задержка окажется меньшей и обычно имеем информацию о максимальном времени задержки элемента данного типа, не зная реальную задержку конкретного элемента, ни его минимальное время задержки. При изменении температуры и старении задержки различных элементов изменяются с разной скоростью, и по этому поводу никто, как правило, никаких гарантий не дает.

Распространены три метода борьбы с гонками: введение тактирования, построение противогоночных схем и учет минимального времени задержки. Наиболее

универсальным, эффективным и поэтому широко используемым методом борьбы с гонками является тактирование [1].

В данной статье рассматривается определение параметров системы синхронизации тактированных дискретных схем при различных предположениях относительно границ изменения задержек компонентов устройства для целей ее диагностирования. Это позволяет построить характеристические значения частоты (допустимые отклонения) работы элементов (триггеров) устройства [2]. Использована общая модель ошибок синхронизации [3,4].

# Общая модель ошибок синхронизации

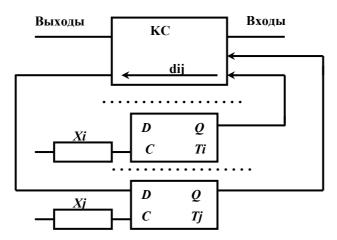

На рис.1. изображена общая схема синхронного цифрового автомата с единой синхронизацией от центрального тактового генератора. Рассмотрим общие случаи ошибок синхронизации, считая, что триггеры переключаются по положительному фронту. Пусть  $X_i$  -задержка срабатывания триггера  $T_i$ , по отношению к генератору и  $d_{ij}$  - задержка сигнала от триггера  $T_i$  к триггеру  $T_j$ , при прохождении его через комбинационную схему (КС) устройства.

Если  $X_j > X_i + d_{ij}$ , то при достижении положительного фронта триггера  $T_i$  данные по более быстрому пути уничтожают данные входа триггера  $T_j$ , прежде чем синхросигнал достигнет его. Поэтому, когда синхросигнал достигает  $T_j$ , ошибочные данные записываются в него. Поскольку данные проходят два триггера за один такт синхронизации, эту ошибку назовем ошибкой двойной синхронизации (double-clocking) [3,4].

Рис. 1.- Общая схема синхронного цифрового автомата с единой синхронизацией.

Под нулевой синхронизацией (zero-clocking) будем понимать случай ошибочной синхронизации, когда данные достигают триггера слишком поздно относительно следующего фронта. Это происходит при  $X_i$  +  $d_{ij}$  >  $X_j$  +  $P_i$  где P — период синхронизации.

Заранее оговорим тот факт, что внешние входы и выходы для нашей модели соединены с исследуемой схемой через внешние триггеры, задержками которых мы не можем управлять, они управляются центральным источником синхросигналов через собственные линии синхронизации. Поэтому можно считать, что в устройстве есть K внутренних триггеров и N - K внешних триггеров, ассоциируемых с внешними

полюсами. Задержки последних полагаем константами.

Общая модель неравенств для временных параметров системы синхронизации дискретных устройств базируется на основополагающем принципе, что минимальное значение периода тактового сигнала должно быть не меньше максимального времени переходного процесса в КС синхронного автомата [1,5], и строится при предположениях:

- а) триггеры  $T_i$  как элементы памяти срабатывают с задержкой  $X_i$  по отношению к сигналам центрального синхрогенератора. В зависимости от технологии, существует минимальное время задержки т, т.е. при i=1, K,  $X_i \geq m$ . Поэтому мы можем описать некоторую неопределенность задержек синхросигнала путем введения линейной зависимости задержки текущего (рассматриваемого в данный момент времени) фронта синхронизации X от номинальной  $X_i$ , т.е. определить параметры a, b ( $0 < a \leq 1 \leq b$ ) такие, что  $aX_i \leq X \leq bX_i$ ;

- б) если фронт синхросигнала приходит в момент X, то для корректной работы триггера необходимо, чтобы входные данные должны быть стабильными в интервале (X-SET, X+HOLD), где SET(HOLD) время установки (удержания);

- в) для исключения двойной синхронизации между  $T_i$ ,  $T_j$ , данные из  $T_i$ , записанные по синхросигналу, должны достигать триггера  $T_j$  не быстрее, чем за время, состоящее из периода удержания HOLD и времени самого медленного прохождения синхросигнала к  $T_j$ . Минимальное время срабатывания  $T_i$  есть  $aX_i$ , а минимальное время прохождения сигнала от  $T_i$  к  $T_j$ , обозначим через s(i,j). Максимальное время задержки срабатывания  $T_i$  есть  $bX_i$ . Поэтому имеем:

$$aX_i + s(i,j) \ge bX_i + HOLD$$

для  $i,j = 1, N$ .

г) для исключения ошибки нулевой синхронизации, данные из  $T_i$ , записанныефронтом синхросигнала, должны достичь  $T_i$  не позже, чем за время установки SET и максимального времени срабатывания  $T_i$  перед следующим фронтом. Максимальное время задержки срабатывания  $T_i$ , есть  $bX_i$ , а максимальное время распространения сигнала от  $T_i$  к  $T_j$  обозначим S(i,j). Минимальное время прибытия фронта для  $T_j$  есть  $P+aX_j$ . Следовательно,  $bX_i+SET+S(i,j)\leq P+aX_j$  для i,j=1, N. Общая модель ограничений временных параметров для системы синхронизации дискретного устройства имеет вид:

$$aX_{i}$$

-  $bX_{j} \geq HOLD$  -  $s(i,j)$  при  $i,j = 1, N$ ,  $aX_{j}$  -  $bX_{i} \geq SET$ +  $S(i,j)$  -  $P$  при  $i,j = 1, N$  (1) и  $X_{i} \geq m$  при  $i = 1, K$ .

Добавим, что если путь от i к j не существует, то полагаем  $s(i,j) = +\infty$ , а  $S(i,j) = -\infty$ , этим мы обеспечиваем для таких триггеров заведомую выполнимость неравенств (1).

Описанные соотношения являются ограничениями для области допустимых решений при расчете периода синхронизации P для выбираемого пользователем критерия оптимизации  $Cr = Cr(P, \overline{Y})$ , где  $\overline{Y}$ , являясь вектором параметров целевой функции, может включать  $\overline{X}$  - $(X_1, X_2, ..., X_K)$ ,  $\overline{S} = (S(i,j), i,j=1,N)$ ,  $\overline{S} = (S(i,j), i,j=1,N)$  и т.п.

На предложенной модели [3,4] можно решать следующие задачи:

а) определение максимального быстродействия устройства, т.е. определение min P при ограничениях (1), что является решением задачи линейного

программирования (ЛП) минимизации периода Р.

б)определение наиболее «надежной» системы синхронизации при заданном P. Критерием этой «надежности» является число M, которое максимизируется при условии, что левые части главных линейных неравенств в (1) больше, чем правые, по крайней мере на M. Поэтому переменная M вычитается из левых частей (1). Следовательно, имеем задачу ЛП: определить  $max\ M$  при таких ограничениях:

$$aX_i$$

-  $bX_j$  -  $M \geq HOLD$  -  $s(i,j)$  при  $i,j=1,N,$   $aX_j$  -  $bX_i$  -  $M \geq SET$ +  $S(i,j)$  -  $P$  при  $i,j=1,N$  и  $X_i \geq m$  при  $i=1,K$  для заданного  $P$ .

в) известной особенностью функционирования триггеров является возможность их зависания, или иначе — метастабильная аномалия их поведения. Интересным с точки зрения повышения надежности устройства является решение задачи с целевой функцией типа  $\max \Sigma C_i X_i - P$  при ограничениях (1). Здесь  $C_i$  — коэффициент приоритетности увеличения времени задержки срабатывания i-го триггера (i = 1, K).

Заметим, что ограничения (1) позволяют сделать следующие выводы относительно величин a, b и P. Суммируя i-е и j-е неравенства, получим для i, j = 1, N:

$$(a - b)(Xi + Xj) \ge 2HOLD - s(i,j) - s(j,j),$$

$(a - b)(X_i + X_j) \ge 2SET + S(i,j) + S(j,i) - 2P.$

Пусть  $s_{i,j} = (s(i,j) + s(j,i))/2$  и  $S_{i,j} = (S(i,j) + S(j,i))/2$ . Ясно, что  $s_{i,j} = s_{j,i}$  и  $S_{i,j} = S_{j,i}$ . Поскольку  $X_i + X_j \ge 2m$  и (a - b)  $(X_i + X_j) \le 0$ , имеем необходимые условия существования системы синхронизации:

$$\min_{i,j} ((s_{i,j} - HOLD)/m) \ge b - a,$$

$$P \ge \max_{i,j} (SET + S_{i,j}) + (b-a)m$$

Эти два соотношения можем записать единым условием сушествования системы синхронизации для выбранной нами модели

$$P \geq \max_{i,j} S_{i,j} - \min_{i,j} s_{i,j} + HOLD + SET + 2 (b-a)m$$

(2)

Считая известными параметры a и b и используя значения задержки элементов на каждом из рассматриваемых путей, вычисляем для каждой пары i,j значения s(i,j), S(i,j). Проблематичной здесь является точная оценка задержки элемента, так как обычно известна только максимальная задержка распространения, а задержки однотипных элементов различаются в значительной степени (соотношение 1:4 и более, [1]). Точное определение задержек должно учитывать множество параметров, среди которых можно выделить такие: температура окружающей среды, колебания напряжения питания, емкость нагрузки, число разветвлений выхода (число подключенных элементов) и т.п. Поэтому при вычислении s(i,j), S(i,j) необходимо вместо максимальной задержки использовать величину, значение которой определяется в зависимости от упомянутых параметров. Если известна минимальная задержка элемента, можно заменить этим значением максимальную задержку при вычислении s(i,j). Однако динамические параметры микросхемы (например, приращение среднего времени задержки распространения сигнала на один незадействованный вход логического элемента или на одну единичную нагрузку, подключаемую на выход) как

основной справочный материал в технических условиях для нее могут отсутствовать. Целесообразно для расчетов на компьютере оценивать задержки максимального и минимального путей выражениями Ls(i,j) и HS(i,j) соответственно, где коэффициенты L и H меньше 1, и производить анализ решений упомянутых задач при различных значениях L, H.

Расчет системы синхронизации схемы при использовании статистических характеристик задержек ее компонентов сводится к вышерассмотренным вариантам с некоторой доверительной вероятностью. Более точная оценка s(i,j) и S(i,j) может быть дана после детального анализа источников задержек прохождения сигнала.

В системе ИКСМ [9, 10] реализован алгоритм автоматического подсчета величин задержек по самому короткому и длинному путям (обычно имеющим максимальное и минимальное количество элементов) для каждой пары триггеров в функциональной схеме проекта. При этом возможны различные варианты их вычисления, связанные с реальной неопределенностью задержек элемента. В [10] рассматривается наиболее простой вариант, когда значением задержки является ее максимум. Исходные данные для этого варианта — таблицы элементов и связей между ними (Элементы и Связи). Основной процедурой алгоритма является определение для заданного триггера I значений максимального (минимального) путей к элементам J(I,J=1,N). Это задача нахождения кратчайшего (максимального) пути между двумя заданными вершинами в ориентированном ациклическом графе, и ее наиболее эффективное решение дает алгоритм Дейкстры [11]. Соответствующий граф строится таким образом: элементы схемы являются вершинами графа, связь между элементами і и j интерпретируется как дуга с весовым коэффициентом  $C_{ii}$ , равным задержке элемента і. Направление задается от входов элементов к выходам. Для превращения графа в ациклический при нахождении кратчайшего (максимального) пути условно обрываем обратные связи на входах (или выходах) триггеров.

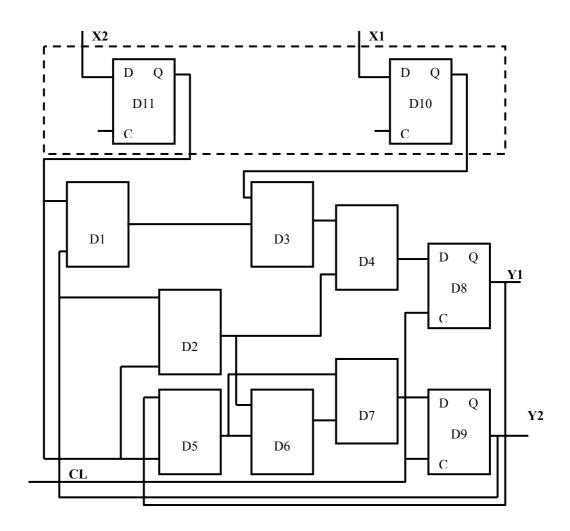

## Пример расчета параметров модели для целей диагностики

Использование системы неравенств описанной модели для целей диагностики основывается на предположении, что старение компонентов и изменения характеристик внешней среды (температуры и т.п.) влияет в первую очередь на изменение параметров переключения триггеров имеющих малый допуск в условиях своего функционирования в устройстве для заданной частоты его работы. Определение этих наиболее "уязвимых" триггеров сводится к определению  $max\ X$  и  $min\ X$  для заданной частоты т.е. для определенного Р. Для примера на рис. 2 выделены штриховой линией фиктивные триггеры с постоянной фиксированной задержкой, ассоциируемые со входами устройства. Фиксация значения задержки отражает неуправляемость задержки входных полюсов, т.е. их внешний характер по отношению рассматриваемому устройству. Результатом определения минимальных максимальных путей для схемы, изображенной на рис.2, являются значения s(2,8) = 12, s(2,9) = 16, s(8,9) = 10, s(9,8) = 6, s(9,9) = 15, s(8,9) = 15, s(9,8) = 7, s(9,9) = 15. При этом считаем, что задержки всех вентилей равны 5, кроме элементов **D1,D3,D4** у которых они равны 2.

Для схемы на рис. 2 система неравенств (1) имеет вид:

$$aX_2 - bX_8 \ge HOLD - s(2,8),$$

$(a - b)X_9 \ge HOLD - s(9,9),$   $aX_2 - bX_9 \ge HOLD - s(2,9),$   $aX_8 - bX_9 \ge HOLD - s(8,9),$

$$aX_9 - bX_8 \ge HOLD - s(9,8),$$

$aX_9 - bX_8 + P \ge SET + S(9,8),$   $aX_8 - bX_9 + P \ge SET + S(8,9),$   $(a - b) X_9 + P \ge SET + S(9,9),$   $CAPPER = APPER = APPER$

Определение  $\min X_i$  ( $\max X_i$ ) при заданном P и условиях (1) позволяет определить диапазон варьирования времени переключения триггера и на этом основании диагностировать в первую очередь триггера с меньшим диапазоном .

Пусть *SET* и *HOLD* равны 1, m - 12, а задержки внешних полюсов  $X_1$ ,  $X_2$  (т.е. триггеров *D10*, *D11*) — 6 (*CL* - синхровход, *Y1*, *Y2* - выходы). При решении задачи с начальными условиями для (a, b), принимающих значения (0.9, 1.1), при P равным 25 имеем диапазон для  $X_8$  (12, 14.9) и для  $X_9$  (12, 18.546). При этом значения  $X_9$  изменяются с 12.67 до 18 и  $X_8$  с 14.36 до 14.9 соответственно. Поэтому критичным узлом является триггер  $D_8$ .

Рис. 2 - Функциональная схема проекта.

### Заключение

На основе использования общей модели системы синхронизации решена задача определения критичных узлов дискретного устройства для целей диагностирования. Критерием выбора является минимум длины диапазона частот переключения узла, при котором обеспечиваются необходимые условия функционирования системы синхронизации цифрового устройства.

# Литература

- 1. Потемкин И.С. Функциональные узлы цифровой автоматики. М: Энергоатомиздат, 1988. 320 с.

- 2. Изерманн Р. Перспективные методы контроля, обнаружения и диагностики неисправностей и их применение//Приборы и системы управления.- 1998. N 4. C. 56-71.

- 3. Fishburn J.P. Clock skew optimization // <u>IEEE</u> Trans. on Computers. 1990. № 7. P. 945 951.

- 4. Gotten L. W. Circuit implementation on high-speed pipiline system. Proc. AFIPS, 1965. 27. P. 489 504.

- 5. Пухальский Г.И., Новосельцева Т.Я. Проектирование дискретных устройств на интегральных микросхемах: Справочник. М.: Радио и связь, 1990. 304 с.

- 6. Kleeman R. The jitter model for metastability and its application to redundant synchronazers // IEEE Trans. on Computers. 1990. № 7. P. 930-942.

- 7. El-Amawy A., Naraghi\_Pour M, Hedge M. Noise modelling effects in redundant synchronizers // Ibid. 1993. -№ 12. P. 1487 1494.

- 8. Marino L. R. General theory of metastable operation // Ibid. 1981. № 2. P. 107-115.

- 9. Андрюхин А.И., Сперанский Д.В. Иерархическая компилятивная система моделирования и генерации тестов // Техническая диагностика и неразрушающий контроль. -1994. №2. С. 71-78.

- 10. Андрюхин А.И. Реализация компилятивного логического моделирования с задержками // Электронное моделирование. 1995. № 2. С. 66-69.

- 11. Кристофидес Н. Теория графов. Алгоритмический подход. М.: Мир, 1978. 432 с.

- 12. Лазер ИМ., Шубарев ВА. Устойчивость цифровых микроэлектронных устройств. М.: Радио и связь. 1983.- 216 с.

- 13. Андрюхин А.И. Задачи синхронизации дискретных устройств// Управляющие системы и машины.-1998. N 6. -C. 36 41.

Поступила в редакційну колегію 20.11.2002